Figure 1. The Physic Photo of AT8254

### **FEATURES**

High-Precision Voltage Detection for Each Cell

Overcharge Detection Voltage n (n = 1 to 4): 3.90V to  $4.35V \pm 25mV$

Overcharge Release Voltage n (n = 1 to 4): 3.80V to  $4.15V \pm 80mV$

Overdischarge Detection Voltage n (n = 1 to 4): 2.3V to  $2.7V \pm 80mV$

Overdischarge Release Voltage n (n = 1 to 4): 2.7V to  $3.0V \pm 100mV$

3-level Overcurrent Protection

Overcurrent Detection Voltage 1:  $0.20V \pm 25mV$ Overcurrent Detection Voltage 2:  $0.50V \pm 100mV$ Overcurrent Detection Voltage 3: VC1 -  $1.1V \pm 300mV$

- The delay times for disovercharge detection, overcharge detection, and overcurrent detection 1 can be set by external capacitors, while the delay times for overcurrent detection 2 and 3 are internally fixed.

- Charging and discharging operation can be controlled through the control terminals.

- Using high-voltage resistant components with an absolute maximum rating of 26V.

- Wide Operating Voltage Range: 3V to 24V

- Wide Operating Temperature Range: -40°C~85°C

- Low Current Consumption

- 30µA max. @ working state &  $T_A$ = 25°C

- 0.1µA max. @ standby state & T<sub>A</sub>= 25°C

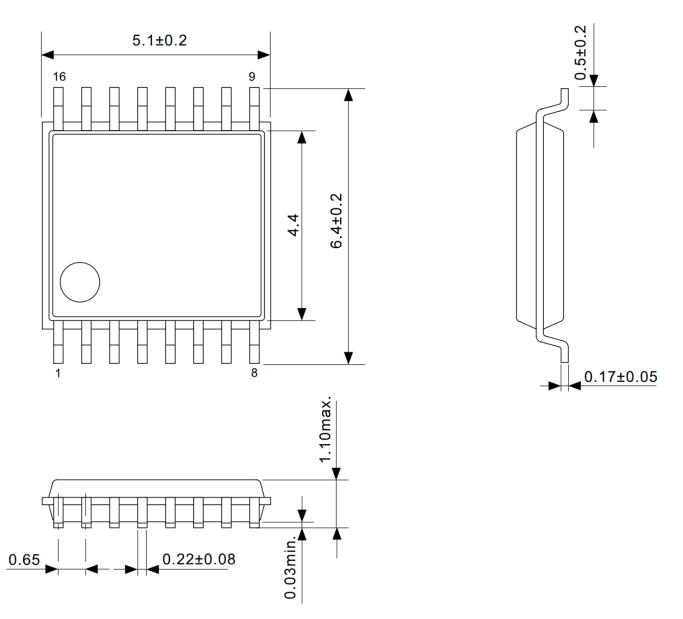

- TSSOP-16 Package

### **APPLICATIONS**

- Lithium-Ion Rechargeable Battery Pack

- Lithium Polymer Rechargeable Battery Pack

### DESCRIPTION

The AT8254 series is a protection integrated circuit designed for 3-series or 4-series lithium-ion/lithium polymer rechargeable batteries, including a high precision voltage detector and delay circuit. The AT8254 series can switch between protecting 3-series or 4-series batteries by using the SEL pin.

### **ABSOLUTE MAXIMUM RATINGS**

- VDD VSS: VSS 0.3V ~ VSS + 26V

- VMP: VSS 0.3V ~ VSS + 26V

- DOP: VSS 0.3V ~ VDD + 0.3V

- COP: VSS 0.3V ~ VSS + 26V

- Other: VSS 0.3V ~ VDD + 0.3V

- Power Dissipation: 400mW

- Operating Temperature Range: -40°C ~ 85°C

- Storage Temperature Range: -40°C ~ 125°C

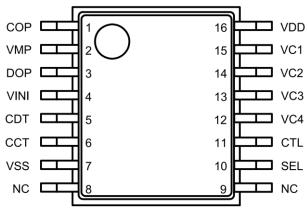

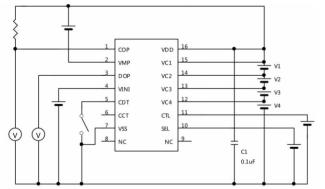

### **PIN CONFIGURATIONS**

Figure 2. Pin Configuration

www.analogtechnologies.com Sales: sales@analogti.com Help Improve Datasheet: datasheet@analogti.com Tel.: (408) 748-9100 ©Copyrights 2000-2024, Analog Technologies, Inc. All Rights Reserved. Updated on 2/29/2024 1161 Ringwood Ct, #110, San Jose, CA 95131, U. S. A. 1

# **PIN DESCRIPTION**

#### Table 1: Pin Function

| Pin # | Symbol | Description                                                                                      |  |  |  |  |  |

|-------|--------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1     | COP    | MOSFET gate connection pin for charge control (N-channel open-drain output).                     |  |  |  |  |  |

| 2     | VMP    | Voltage detection pin between VC1 and VMP (Pin for overcurrent detection 3).                     |  |  |  |  |  |

| 3     | DOP    | MOSFET gate connection pin for discharge control (CMOS output).                                  |  |  |  |  |  |

| 4     | VINI   | Voltage detection pin between VSS and VINI (Pin for overcurrent detection 1, 2).                 |  |  |  |  |  |

| 5     | CDT    | Capacitor connection for overdischarge detection delay and overcurrent detection 1 delay.        |  |  |  |  |  |

| 6     | ССТ    | Capacitor connection pin for overcharge detection delay.                                         |  |  |  |  |  |

| 7     | VSS    | Input pin for negative power supply, connection pin for battery 4's negative voltage.            |  |  |  |  |  |

| 8     | NC     | No connection.                                                                                   |  |  |  |  |  |

| 9     | NC     | No connection.                                                                                   |  |  |  |  |  |

| 10    | SEL    | Pin for switching 3-series or 4-series cell. VSS level: 3-series cell, VDD level: 4-series cell. |  |  |  |  |  |

| 11    | CTL    | Control pin for the charging MOSFET and the discharging MOSFET.                                  |  |  |  |  |  |

| 12    | VC4    | Connection pin for battery 3's negative input & battery 4's positive input.                      |  |  |  |  |  |

| 13    | VC3    | Connection pin for battery 2's negative input & battery 3's positive input.                      |  |  |  |  |  |

| 14    | VC2    | Connection pin for battery 1's negative input & battery 2's positive input.                      |  |  |  |  |  |

| 15    | VC1    | Connection pin for battery 1's positive input.                                                   |  |  |  |  |  |

| 16    | VDD    | Input pin for positive power supply, connection pin for battery 1's positive voltage.            |  |  |  |  |  |

AT8254

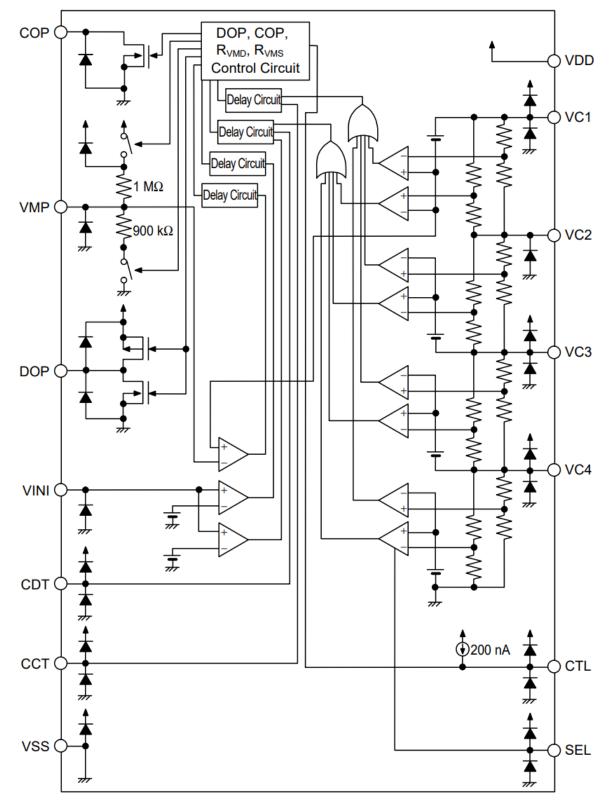

### **BLOCK DIAGRAM**

## **ELECTRICAL CHARACTERISTICS**

#### (At $T_A = +25^{\circ}C$ , $V_{IN} = 12V$ , unless otherwise noted.)

#### Table 3.

| Parameter                                            | Symbol            | Test Conditions                  | Min.                     | Тур.                 | Max.                     | Unit | Test<br>Circuit |

|------------------------------------------------------|-------------------|----------------------------------|--------------------------|----------------------|--------------------------|------|-----------------|

| Detection Voltage                                    |                   |                                  |                          |                      |                          |      |                 |

| Overcharge detection voltage n $(n = 1, 2, 3, 4)$    | VCUn              |                                  | V <sub>CUn</sub> -0.025  | VCUn                 | V <sub>CUn</sub> +0.025  | V    | 2               |

| Overcharge release voltage n<br>(n = 1, 2, 3, 4)     | V <sub>CLn</sub>  |                                  | V <sub>CLn</sub> -0.08   | $V_{\text{CLn}}$     | V <sub>CLn</sub> +0.08   | V    | 2               |

| Overdischarge detection voltage n $(n = 1, 2, 3, 4)$ | VDLn              |                                  | V <sub>DLn</sub> -0.08   | $V_{DLn}$            | V <sub>DLn</sub> +0.08   | V    | 2               |

| Overdischarge release voltage n $(n = 1, 2, 3, 4)$   | V <sub>DUn</sub>  |                                  | V <sub>DUn</sub> -0.10   | $V_{DUn}$            | V <sub>DUn</sub> +0.10   | ۷    | 2               |

| Overcurrent detection voltage 1                      | V <sub>IOV1</sub> |                                  | V <sub>IOV1</sub> -0.025 | V <sub>IOV1</sub>    | V <sub>IOV1</sub> +0.025 | V    | 2               |

| Overcurrent detection voltage 2                      | V <sub>IOV2</sub> |                                  | 0.4                      | 0.5                  | 0.6                      | V    | 2               |

| Overcurrent detection voltage 3                      | V <sub>IOV3</sub> |                                  | V <sub>C1</sub> -1.5     | V <sub>C1</sub> -1.2 | V <sub>C1</sub> -0.9     | V    | 2               |

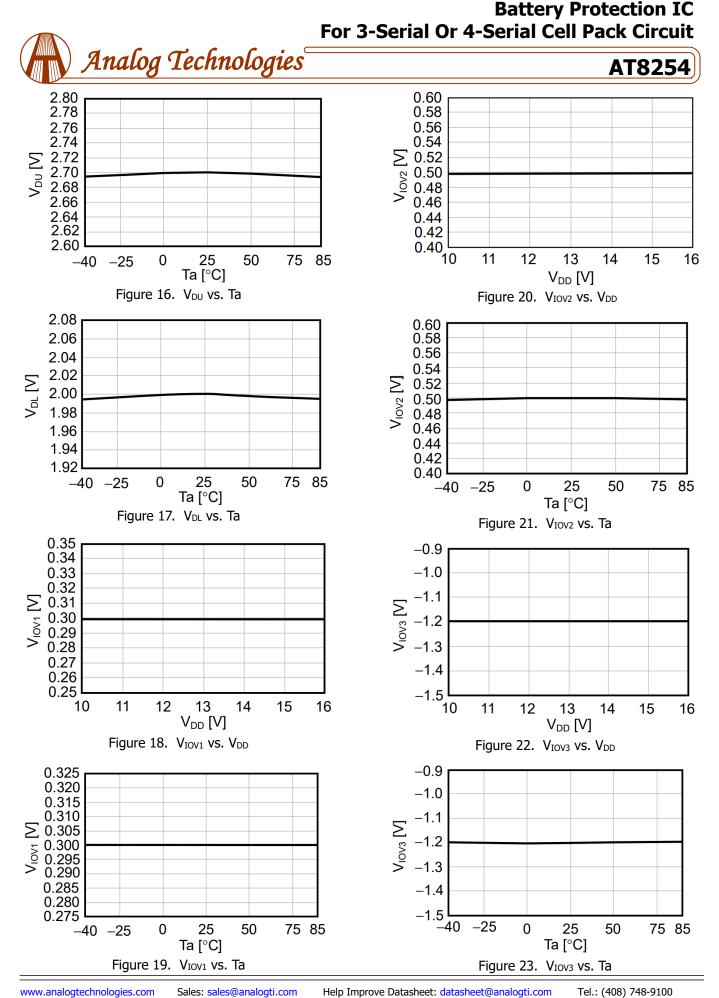

| Delay Time                                           |                   |                                  |                          |                      |                          |      |                 |

| Overcharge detection delay time                      | t <sub>cu</sub>   | CCT pin<br>capacitance = 0.1µF   | 0.5                      | 1.0                  | 1.5                      | S    | 3               |

| Overdischarge detection delay time                   | tol               | CDT pin<br>capacitance = 0.1µF   | 50                       | 100                  | 150                      | ms   | 3               |

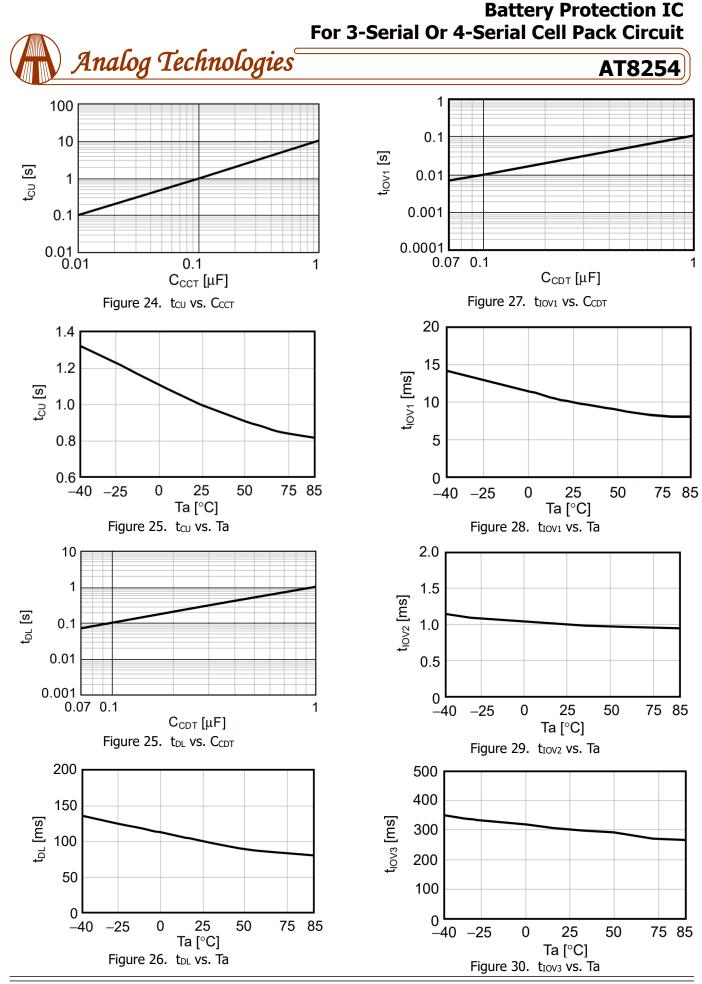

| Overcurrent detection delay time 1                   | t <sub>IOV1</sub> | CDT pin<br>capacitance = 0.1µF   | 5                        | 10                   | 15                       | ms   | 3               |

| Overcurrent detection delay time 2                   | t <sub>IOV2</sub> |                                  | 0.4                      | 1                    | 1.6                      | ms   | 3               |

| Overcurrent detection delay time 3                   | t <sub>IOV3</sub> | FET gate<br>capacitance = 2000pF | 100                      | 300                  | 600                      | μs   | 3               |

| 0V Battery Charge                                    |                   |                                  |                          |                      |                          |      |                 |

| 0 V battery charge starting charger voltage          | V <sub>0CHA</sub> | 0 V battery charge<br>enabled    |                          | 0.8                  | 1.5                      | V    | 4               |

| 0 V battery charge inhibition<br>battery voltage     | VOINH             | 0 V battery charge<br>inhibited  | 0.4                      | 0.7                  | 1.1                      | V    | 4               |

| Internal Resistance                                  |                   |                                  |                          |                      |                          |      |                 |

| Resistance between VMP and VDD                       | Rvmd              |                                  | 0.5                      | 1                    | 1.5                      | MΩ   | 5               |

| Resistance between VMP and VSS                       | Rvms              |                                  | 450                      | 900                  | 1800                     | kΩ   | 5               |

www.analogtechnologies.com Sales: sales@analogti.com Help Improve Datasheet: datasheet@analogti.com Tel.: (408) 748-9100

AT8254

| Parameter                                | Symbol            | Test Conditions                                        | Min.                 | Тур. | Max.                 | Unit | Test<br>Circuit |

|------------------------------------------|-------------------|--------------------------------------------------------|----------------------|------|----------------------|------|-----------------|

| Input Voltage                            |                   |                                                        |                      |      |                      |      |                 |

| Operating voltage between VDD<br>and VSS | VDSOP             | Output voltage of DOP and COP fixed                    | 3                    |      | 24                   | V    | 2               |

| CTL input voltage "H"                    | VCTLH             |                                                        | V <sub>DD</sub> ×0.8 |      |                      | v    | 2               |

| CTL input voltage "L"                    | V <sub>CTLL</sub> |                                                        |                      |      | V <sub>DD</sub> ×0.2 | V    | 2               |

| SEL input voltage "H"                    | VSELH             |                                                        | V <sub>DD</sub> ×0.8 |      |                      | v    | 2               |

| SEL input voltage "L"                    | VSELL             |                                                        |                      |      | vdd×0.2              | V    | 2               |

| Input Current                            |                   |                                                        |                      |      |                      |      |                 |

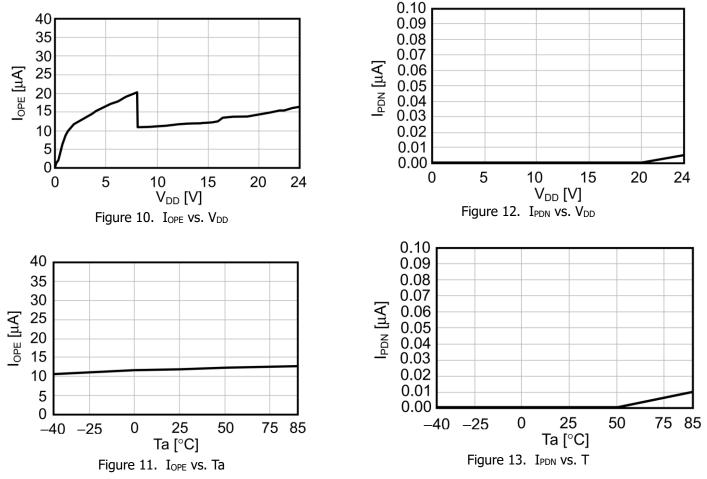

| Current consumption during operation     | I <sub>OPE</sub>  | V1=V2=V3=V4=3.5V                                       |                      | 12   | 30                   | μA   | 1               |

| Current consumption during power-down    | I <sub>PDN</sub>  | V1=V2=V3=V4=1.5V                                       |                      |      | 0.1                  | μA   | 1               |

| VC1 pin current                          | I <sub>VC1</sub>  | V1=V2=V3=V4=3.5V                                       |                      | 1.5  | 3                    | μA   | 5               |

| VC2 pin current                          | I <sub>VC2</sub>  | V1=V2=V3=V4=3.5V                                       | -0.3                 | 0    | 0.3                  | μA   | 5               |

| VC3 pin current                          | I <sub>VC3</sub>  | V1=V2=V3=V4=3.5V                                       | -0.3                 | 0    | 0.3                  | μA   | 5               |

| VC4 pin current                          | I <sub>VC4</sub>  | V1=V2=V3=V4=3.5V                                       | -0.3                 | 0    | 0.3                  | μA   | 5               |

| CTL pin current "H"                      | Ictlh             | V1=V2=V3=V4=3.5V<br>V <sub>CTL</sub> = V <sub>DD</sub> |                      |      | 0.1                  | μA   | 5               |

| CTL pin current "L"                      | I <sub>CTLL</sub> | V1=V2=V3=V4=3.5V<br>$V_{CTL} = V_{SS}$                 | -0.4                 | -0.2 |                      | μA   | 5               |

| SEL pin current "H"                      | Iselh             | $V1=V2=V3=V4=3.5V$ $V_{SEL} = V_{DD}$                  |                      |      | 0.1                  | μA   | 5               |

| SEL pin current "L"                      | Isell             | V1=V2=V3=V4=3.5V<br>V <sub>SEL</sub> = V <sub>SS</sub> | 0.1                  |      |                      | μA   | 5               |

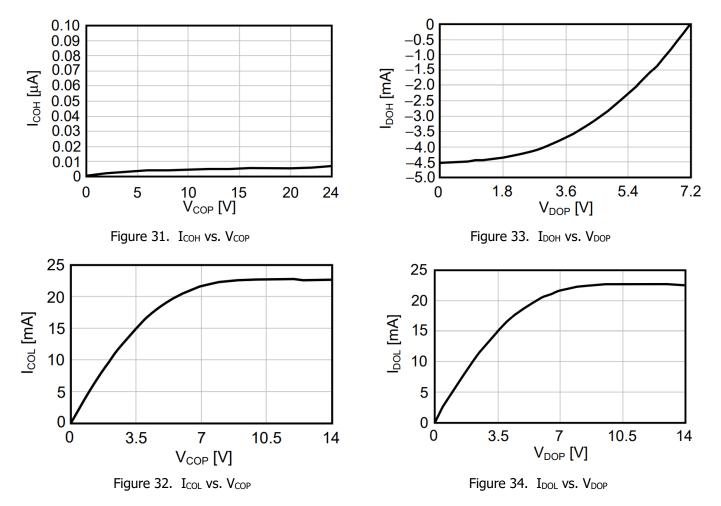

| Output Current                           |                   |                                                        |                      |      |                      |      |                 |

| COP pin leakage current                  | I <sub>сон</sub>  | $V_{COP} = 24V$                                        |                      |      | 0.1                  | μA   | 5               |

| COP pin sink current                     | ICOL              | $V_{COP} = V_{SS} + 0.5V$                              | 10                   |      |                      | μA   | 5               |

| DOP pin source current                   | I <sub>DOH</sub>  | $V_{\text{DOP}} = V_{\text{DD}} - 0.5V$                | 10                   |      |                      | μA   | 5               |

| DOP pin sink current                     | I <sub>DOL</sub>  | $V_{\text{DOP}} = V_{\text{SS}} + 0.5 V$               | 10                   |      |                      | μA   | 5               |

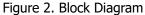

### **TEST CIRCUITS**

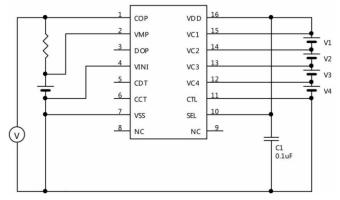

#### 1. Current Consumption during Operation & Current Consumption during Power-down

(Test circuit 1)

The current at the VSS pin is the current consumption during operation (IOPE), when V1 = V2 = V3 = V4 = 3.5V and  $V_{VMP} = V_{DD}$ .

The current at the VSS pin is the current consumption during power-down (IPDN), when V1 = V2 = V3 = V4 = 1.5V and  $V_{VMP} = V_{SS}$ .

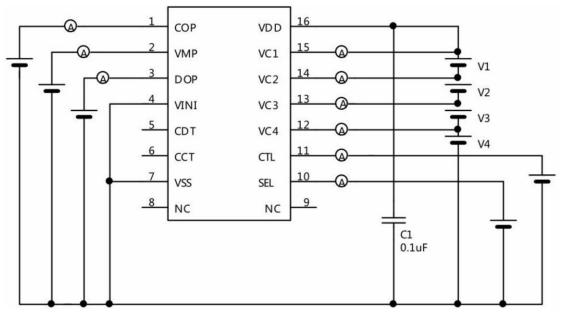

2. Overcharge Detection Voltage, Overcharge Release Voltage, Overdischarge Detection Voltage, Overdischarge Release Voltage, Overcurrent Detection Voltage 1, Overcurrent Detection Voltage 2, Overcurrent Detection Voltage 3, CTL Input Voltage "H", CTL Input Voltage "L", SEL Input Voltage "H", SEL Input Voltage "L".

(Test circuit 2)

Confirm that the COP pin and DOP pin are low ( $V_{DD} \times 0.1V$  or lower) when  $V_{VMP} = V_{SEL} = V_{DD}$ ,  $V_{INI} = V_{CTL} = V_{SS}$ , the CCT pin is open, the CDT pin is open, and V1 = V2 = V3 = V4 = 3.5V (this status is referred to as the initial status).

• Overcharge Detection Voltage (V<sub>CU1</sub>), Overcharge Release Voltage (V<sub>CL1</sub>)

The overcharge detection voltage (V<sub>CU1</sub>) is the voltage of V1 when the voltage of the COP pin is "H" (VDD  $\times$  0.9V or more) after the V1 voltage has been gradually increased starting at the initial status. The overcharge release voltage (V<sub>CL1</sub>) is the voltage of V1 when the voltage at the COP pin is "L" after the V1 voltage has been gradually decreased.

• Overdischarge Detection Voltage (V<sub>DL1</sub>), Overdischarge Release Voltage (V<sub>DU1</sub>)

The overdischarge detection voltage ( $V_{DL1}$ ) is the voltage of V1 when the voltage of the DOP pin is "H" after the V1 voltage has been gradually decreased starting at the initial status. The overdischarge release voltage ( $V_{DU1}$ ) is the voltage of V1 when the voltage at the DOP pin is "L" after the V1 voltage has been gradually increased. When the voltage of Vn (n = 2 to 4) is changed, the overcharge detection voltage ( $V_{CUn}$ ), overcharge release voltage ( $V_{CLn}$ ), overdischarge detection voltage ( $V_{DLn}$ ), and overdischarge release voltage ( $V_{DU1}$ ) can be determined in the same way as when n = 1.

• Overcurrent Detection Voltage 1 (VIOV1)

Overcurrent detection voltage 1 ( $V_{IOV1}$ ) is the voltage of the VINI pin when the voltage of the DOP pin is "H" after the VINI pin voltage has been gradually increased starting at the initial status.

• Overcurrent Detection Voltage 2 (V<sub>IOV2</sub>)

Overcurrent detection voltage 2 ( $V_{IOV2}$ ) is the voltage of the VINI pin when the voltage of the DOP pin is "H" after the voltage of the CDT pin was set to  $V_{SS}$  following the initial status and the voltage of the VINI pin has been gradually decreased.

Overcurrent Detection Voltage 3 (VIOV3)

Overcurrent detection voltage 3 ( $V_{IOV3}$ ) is the voltage difference between  $V_{VC1}$  and  $V_{VMP}$  ( $V_{VC1} - V_{VMP}$ ) when the voltage of the DOP pin is "H" after the VMP voltage has been gradually decreased starting at the initial status.

• CTL Input Voltage "H" (VCTLH), CTL Input Voltage "L" (VCTLL)

The CTL input voltage "H" (V<sub>CTLH</sub>) is the voltage of CTL when the voltages at the COP and DOP pins are "H" after the CTL voltage has been gradually increased starting at the initial status. The CTL input voltage "L" (V<sub>CTLL</sub>) is the voltage of CTL when the voltages at the COP and DOP pins are "L" after the CTL voltage has been gradually decreased.

• SEL Input Voltage "H" (VSELH), SEL Input Voltage "L" (VSELL)

AT8254

Apply 0 V to V4 in the initial status and confirm that the DOP pin is "H". The SEL input voltage "L" ( $V_{SELL}$ ) is the voltage of the SEL pin when the voltage at the DOP pin is "L" after the SEL voltage has been gradually decreased. The SEL input voltage "H" ( $V_{SELH}$ ) is the voltage of the SEL pin when the voltage of the DOP pin is "H" after the SEL voltage has been gradually increased.

# 3. Overcharge Detection Delay Time, Overdischarge Detection Delay Time, Overcurrent Detection Delay Time 1, Overcurrent Detection Delay Time 2, Overcurrent Detection Delay Time 3.

(Test circuit 3)

Confirm that the COP pin and DOP pin are "L" when  $V_{VMP} = V_{DD}$ ,  $V_{INI} = V_{SS}$ , and V1 = V2 = V3 = V4 = 3.5V (this status is referred to as the initial status).

• Overcharge Detection Delay Time (t<sub>CU</sub>)

The overcharge detection delay time (tCU) is the time it takes for the voltage of the COP pin to change from "L" to "H" after the voltage of V1 is instantaneously changed to 4.5V from the initial status.

• Overdischarge Detection Delay Time (t<sub>DL</sub>)

The overdischarge detection delay time ( $t_{DL}$ ) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of V1 is instantaneously changed to 1.5V from the initial status.

• Overcurrent Detection Delay Time 1 (t<sup>IOV1</sup>)

Overcurrent detection delay time 1 ( $t_{IOV1}$ ) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VINI pin is instantaneously changed to 0.4V from the initial status.

• Overcurrent Detection Delay Time 2 (t<sub>IOV2</sub>)

Overcurrent detection delay time 2 ( $t_{IOV2}$ ) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VINI pin is instantaneously changed to  $V_{IOV2\_max}$  + 0.2V from the initial status.

Overcurrent Detection Delay Time 3 (t<sub>IOV3</sub>)

Overcurrent detection delay time 3 ( $t_{IOV3}$ ) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VMP pin is instantaneously changed to  $V_{IOV3}$ \_min – 0.2V from the initial status.

# 4. OV Battery Charge Starting Charger Voltage (OV Battery Charge Enabled), OV Battery Charge Inhibition Battery Voltage (OV Battery Charge Inhibited)

(Test circuit 4)

Either the 0V battery charge starting charger voltage or the 0V battery charge inhibition battery voltage is applied to each product according to the 0V battery charge function.

- For the 0 V battery charge starting charger voltage, the COP pin voltage should be lower than  $V_{0CHA_max.} 1V$ when V1 = V2 = V3 = V4 = 0V and  $V_{VMP} = V_{0CHA_max}$ .

- For 0 V battery charge inhibition battery voltage, the COP pin voltage should be higher than  $V_{VMP} 1V$  when  $V1 = V2 = V3 = V4 = V_{0INH_{min}}$  and  $V_{VMP} = 24$  V.

- 5. Resistance between VMP and VDD, Resistance between VMP and VSS, VC1 Pin Current, VC2 Pin Current, VC3 Pin Current, VC4 Pin Current, CTL pin Current "H", CTL Pin Current "L", SEL Pin Current "H", SEL Pin Current "L", COP Pin Leakage Current, COP Pin Sink Current, DOP Pin Source Current, DOP Pin Sink Current.

#### (Test circuit 5)

$V_{VMP} = V_{SEL} = V_{DD}$ ,  $V_{INI} = V_{CTL} = V_{SS}$ , V1 = V2 = V3 = V4 = 3.5V, and other pins left "open" (this status is referred to as the initial status).

• The resistance between VMP and VDD ( $R_{VMD}$ ) is obtained from  $R_{VMD} = V_{DD} / I_{VMD}$  using the current value of the VMP pin ( $I_{VMD}$ ) when  $V_{VMP} = V_{SS}$  after the initial status.

AT8254

- The resistance between VMP and VSS ( $R_{VMS}$ ) is obtained from  $R_{VMS} = V_{DD} / I_{VMS}$  using the current value of the VMP pin ( $_{IVMS}$ ) when V1 = V2 = V3 = V4 = 1.8V after the initial status.

- At the initial status, the current that flows through the VC1 pin is the VC1 pin current ( $I_{VC1}$ ), the current that flows through the VC2 pin is the VC2 pin current ( $I_{VC2}$ ), the current that flows through the VC3 pin is the VC3 pin current ( $I_{VC3}$ ), and the current that flows through the VC4 pin is the VC4 pin current ( $I_{VC4}$ ).

- In the initial status, the current that flows through the CTL pin is the CTL pin current "L" (I<sub>CTLL</sub>), after that, when V<sub>CTL</sub> = V<sub>DD</sub>, the current that flows through the CTL pin is the CTL pin current "H" (I<sub>CTLH</sub>).

- In the initial status, the current that flows through the SEL pin is the SEL pin current "H" ( $I_{SELH}$ ), after that, when  $V_{SEL} = V_{SS}$ , the current that flows through the SEL pin is the SEL pin current "L" ( $I_{SELL}$ ).

- The COP pin sink current ( $I_{COL}$ ) is the current that flows through the COP pin when  $V_{COP} = V_{SS} + 0.5V$  after the initial status. After that, the current that flows through the COP pin when V1 = V2 = V3 = V4 = 6V and  $V_{COP} = V_{DD}$  is the COP pin leakage current ( $I_{COH}$ ).

- The DOP pin sink current ( $I_{DOL}$ ) is the current that flows through the DOP pin when  $V_{DOP} = V_{SS} + 0.5V$  after the initial status. After that, the current that flows through the DOP pin when  $V_{VMP} = V_{DD} 2V$  and  $V_{DOP} = V_{DD} 0.5V$  is the DOP pin source current ( $I_{DOH}$ ).

Figure 3. Test Circuit 1

Figure 4. Test Circuit 2

Figure 5. Test Circuit 3

Figure 6. Test Circuit 4

### AT8254

Figure 7. Test Circuit 5

# INSTRUCTION

1. Normal Status

When the voltage of each of the batteries is in the range from  $V_{DLn}$  to  $V_{CUn}$  and the discharge current is lower than the specified value (the VINI pin voltage is lower than  $V_{IOV1}$  and  $V_{IOV2}$ , and the VMP pin voltage is higher than  $V_{IOV3}$ ), the charging and discharging FETs are turned on.

2. Overcharge Status

When the voltage of one of the batteries becomes higher than  $V_{CUn}$  and the state continues for  $t_{CU}$  or longer, the COP pin becomes high impedance. The COP pin is pulled up to the EB+ pin voltage by an external resistor, and the charging FET is turned off to stop charging. This is called the overcharge status. The overcharge status is released when one of the following two conditions holds.

(1). The voltage of each of the batteries becomes  $V_{\mbox{\tiny CLn}}$  or lower.

(2). The voltage of each of the batteries is  $V_{CUn}$  or lower, and the VMP pin voltage is 39/40 × VDD or lower (a load is connected and discharging is started via the body diode of the charging FET).

3. Overdischarge Status

When the voltage of one of the batteries becomes lower than  $V_{DLn}$  and the state continues for  $t_{DL}$  or longer, the DOP pin voltage becomes VDD level, and the discharging FET is turned off to stop discharging. This is called the overdischarge status.

4. Overcurrent Status

The AT8254 Series has three overcurrent detection levels ( $V_{IOV1}$ ,  $V_{IOV2}$ , and  $V_{IOV3}$ ) and three overcurrent detection delay times ( $t_{IOV1}$ ,  $t_{IOV2}$ , and  $t_{IOV3}$ ) corresponding to each overcurrent detection level. When the discharging current becomes higher than the specified value (the voltage between VSS and VINI is greater than  $V_{IOV1}$ ) and the state continues for  $t_{IOV1}$  or longer, the AT8254 Series enters the overcurrent status, in which the DOP pin voltage becomes VDD level to turn off the discharging FET to stop discharging, the COP pin becomes high impedance and is pulled up to the EB+ pin voltage to turn off the charging FET to stop charging, and the VMP pin is pulled up to the VDD voltage by the internal resistor ( $R_{VMD}$ ). Operation of overcurrent detection level 2 ( $V_{IOV2}$ ) and overcurrent detection delay time 2 ( $t_{IOV2}$ ) is the same as for  $V_{IOV1}$  and  $t_{IOV1}$ . In the overcurrent status, the VMP pin is pulled up to the VDD level by the internal resistor in the IC (RVMD resistor). The overcurrent status is released when the following condition holds.

(1) The VMP pin voltage is  $V_{IOV3}$  or higher because a charger is connected or the load (30M $\Omega$  or more) is released.

5. Delay Time Setting

The overcharge detection delay time ( $t_{CU}$ ) is determined by the external capacitor connected to the CCT pin. The overdischarge detection delay time ( $t_{DL}$ ) and overcurrent detection delay time 1 ( $t_{IOV1}$ ) are determined by the external capacitor connected to the CDT pin. Overcurrent detection delay times 2 and 3 ( $t_{IOV2}$ ,  $t_{IOV3}$ ) are fixed internally.

min. typ. max.

$t_{CU}[s] = (5.00, 10.0, 15.0) \times C_{CCT}[\mu F]$

$t_{DL}[s] = (0.50, 1.00, 1.50) \times C_{CDT}[\mu F]$

$t_{IOV1}[s] = (0.05, 0.10, 0.15) \times C_{CDT}[\mu F]$

#### 6. Dormant State

When transitioning to over-discharge status, discharge ceases. As the internal RVMS resistor within the IC pulls the VMP terminal to VSS, the voltage on the VMP terminal drops below VDD/2, causing the SLM8254 to enter a dormant state. In this state, nearly all circuits within the SLM8254 stop functioning, reducing the current consumption to below IPDN. The status of each output terminal becomes as follows:

#### (1) COP Hi-Z

(2) DOP VDD

The dormant state is terminated under the following conditions:

- (1) The voltage on the VMP terminal rises above  $V_{DD}/2$  (charger connected).

- (2) All battery voltages rise above  $V_{DLn}$ , and the VDD sub-voltage rises above  $V_{DD}/2$  (charger connected).

- 7. 0V Battery Charge

Regarding charging of the battery after self-discharge (0V battery), the SLM8254 allows charging of the 0V battery (which can be charged to the 0V battery). Caution When the VDD pin voltage is lower than the minimum value of  $V_{DSOP}$ , the operation of the AT8254 Series is not guaranteed.

#### 8. CTL Pin

The AT8254 Series has control pins. The CTL pin is used for controlling the COP and DOP pin output voltages. CTL pin takes precedence over the battery protection circuit.

| CTL  | COP    | DOP    |  |  |

|------|--------|--------|--|--|

| High | Hi-Z   | VDD    |  |  |

| Open | Hi-Z   | VDD    |  |  |

| Low  | Normal | Normal |  |  |

#### 9. SEL pin

The AT8254 Series has control pins. The SEL pin is used for switching between 3-cell and 4-cell protection. When the SEL pin is low, overdischarge detection of the V4 cell is prohibited and an overdischarge is not detected even if the V4 cell is shorted, therefore, this IC can be used for 3-cell protection. The SEL pin takes precedence over the battery protection circuit. Use the SEL pin at high or low.

| SEL    | State             |  |  |  |  |

|--------|-------------------|--|--|--|--|

| 022    | 8446              |  |  |  |  |

| High   | 4-cell protection |  |  |  |  |

| riigii |                   |  |  |  |  |

| Open   | Undefined         |  |  |  |  |

| Open   | Undernied         |  |  |  |  |

| Low    | 2 coll protoction |  |  |  |  |

| Low    | 3-cell protection |  |  |  |  |

|        |                   |  |  |  |  |

AT8254

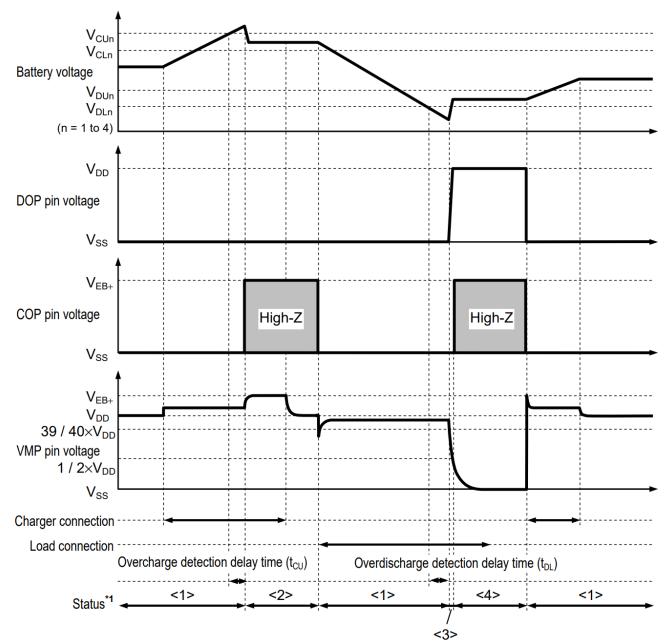

# TIMING CHART

1. Overcharge Detection and Overdischarge Detection

Note:

- (1). Normal status

- (2). Overcharge status

- (3). Overdischarge status

- (4). Power-down status

The charger is assumed to charge with a constant current.  $V_{EB+}$  indicates the open voltage of the charger.

AT8254

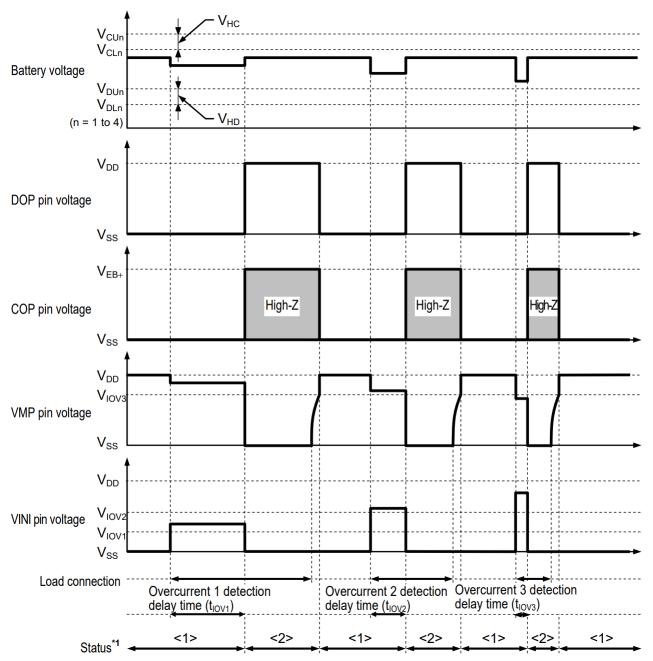

2. Overcurrent Detection

Note:

(1). Normal status

(2). Overcurrent status

The charger is assumed to charge with a constant current.  $V_{EB+}$  indicates the open voltage of the charger.

AT8254

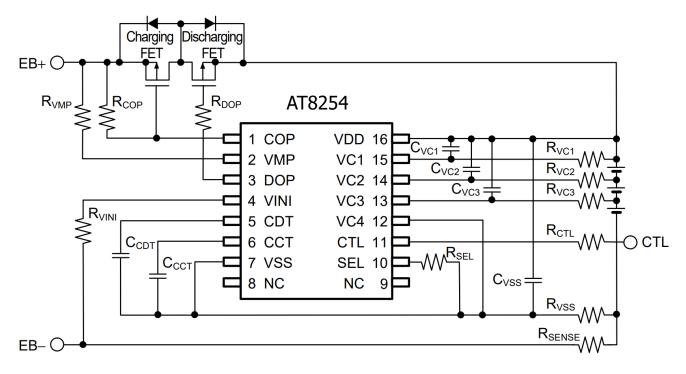

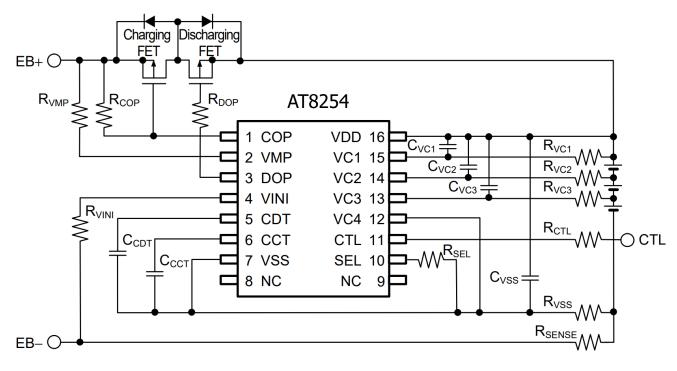

# **TYPICAL APPLICATION**

**3-serial Cell**

Figure 8.

#### 4-serial Cell

#### **Constants for External Components**

| No. | Symbol           | Min. | Тур. | Max. | Unit | No. | Symbol           | Min. | Тур. | Max. | Unit |

|-----|------------------|------|------|------|------|-----|------------------|------|------|------|------|

| 1   | R <sub>VC1</sub> | 0    | 1    | 1    | kΩ   | 11  | Rsense           | 0    | -    | -    | mΩ   |

| 2   | Rvc2             | 0    | 1    | 1    | kΩ   | 12  | Rvss             | 10   | 51   | 51   | Ω    |

| 3   | Rvсз             | 0    | 1    | 1    | kΩ   | 13  | C <sub>VC1</sub> | 0    | 0.1  | 0.33 | μF   |

| 4   | Rvc4             | 0    | 1    | 1    | kΩ   | 14  | C <sub>VC2</sub> | 0    | 0.1  | 0.33 | μF   |

| 5   | R <sub>DOP</sub> | 2    | 5.1  | 10   | kΩ   | 15  | Rvc3             | 0    | 0.1  | 0.33 | μF   |

| 6   | RCOP             | 0.1  | 1    | 1    | MΩ   | 16  | Cvc4             | 0    | 0.1  | 0.33 | μF   |

| 7   | RVMP             | 1    | 5.1  | 10   | kΩ   | 17  | Ссст             | 0.01 | 0.1  | -    | μF   |

| 8   | R <sub>CTL</sub> | 0    | 0    | 100  | kΩ   | 18  | C <sub>CDT</sub> | 0.07 | 0.1  | -    | μF   |

| 9   | Rvini            | 0    | 1    | 100  | kΩ   | 19  | Cvss             | 2.2  | 2.3  | 10   | μF   |

| 10  | R <sub>SEL</sub> | 0    | 0    | 100  | kΩ   |     |                  |      |      |      |      |

Note: Please set up a filter constant to be

$R_{VSS} \times C_{VSS} \ge 51 \ \mu F \bullet \Omega$ ,

and  $R_{VC1} \times C_{VC1} = R_{VC2} \times C_{VC2} = R_{VC3} \times C_{VC3} = R_{VC4} \times C_{VC4} = R_{VSS} \times C_{VSS}$ .

#### Caution

1. The constants may be changed without notice.

2. It is recommended that filter constants between VDD and VSS should be set approximately to 112  $\mu F$  •  $\Omega.$

e.g. CVSS × RVSS = 2.2  $\mu$ F × 51  $\Omega$  = 112  $\mu$ F •  $\Omega$

Enough evaluation of transient power supply variation and overcurrent protection function in the actual application is needed to determine the proper constants. Contact our sales representatives in case the constants should be set to other than 112  $\mu$ F •  $\Omega$  or so.

3. It has not been confirmed whether the operation is normal or not in circuits other than the connection examples. In addition, the connection examples and the constants do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constants.

#### Precautions

• The application conditions for the input voltage, output voltage, and load current should not exceed the package power dissipation.

• Batteries can be connected in any order, however, there may be cases when discharging cannot be performed when a battery is connected. In this case, short the VMP pin and VDD pin or connect the battery charger to return to the normal status.

• When an overcharged battery and an overdischarged battery intermix, the circuit is in both the overcharge and overdischarge statuses, so charging and discharging are not possible.

• Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

### **TYPICAL CHARACTERISTICS**

#### **1. Current Consumption**

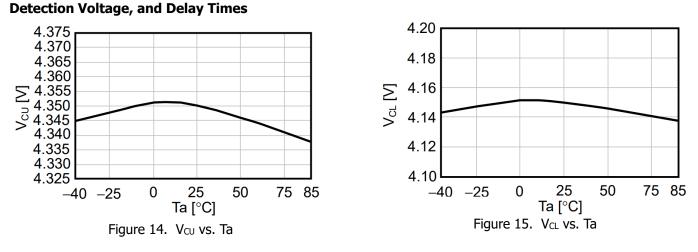

2. Overcharge Detection / Release Voltage, Overdischarge Detection / Release Voltage, Overcurrent

www.analogtechnologies.com Sales: sales@analogti.com Help Improve Datasheet: datasheet@analogti.com Tel.: (408) 748-9100 ©Copyrights 2000-2024, Analog Technologies, Inc. All Rights Reserved. Updated on 2/29/2024 1161 Ringwood Ct, #110, San Jose, CA 95131, U. S. A. 17

#### 3. COP / DOP Pin

AT8254

# **OUTLINE DIMENSIONS**

# **ORDERING INFORMATION**

| Part Number | Buy Now                 |

|-------------|-------------------------|

| AT8254      | <b>()</b> * <b>()</b> * |

- It is important to carefully read and follow the warnings, cautions, and product-specific notes provided with electronic components. These instructions are designed to ensure the safe and proper use of the component and to prevent damage to the component or surrounding equipment. Failure to follow these instructions could result in malfunction or failure of the component, damage to surrounding equipment, or even injury or harm to individuals. Always take the necessary precautions and seek professional assistance if unsure about proper use or handling of electronic components.

- 2. Please note that the products and specifications described in this publication are subject to change without prior notice as we continuously improve our products. Therefore, we recommend checking the product descriptions and specifications before placing an order to ensure that they are still applicable. We also reserve the right to discontinue the production and delivery of certain products, which means that not all products named in this publication may always be available.

- 3. This means that while ATI may provide information about the typical requirements and applications of their products, they cannot guarantee that their products will be suitable for all customer applications. It is the responsibility of the customer to evaluate whether an ATI product with the specified properties is appropriate for their particular application.

- 4. ATI warrants its products to perform according to specifications for one year from the date of sale, except when damaged due to excessive abuse. If a product fails to meet specifications within one year of the sale, it can be exchanged free of charge.

- 5. ATI reserves the right to make changes or discontinue products or services without notice. Customers are advised to obtain the latest information before placing orders.

- 6. All products are sold subject to terms and conditions of sale, including those pertaining to warranty, patent infringement, and limitation of liability. Customers are responsible for their applications using ATI products, and ATI assumes no liability for applications assistance or customer product design.

- 7. ATI does not grant any license, either express or implied, under any patent right, copyright, mask work right, or other intellectual property right of ATI.

- 8. ATI's publication of information regarding third-party products or services does not constitute approval, warranty, or endorsement.

- 9. ATI retains ownership of all rights for special technologies, techniques, and designs for its products and projects, as well as any modifications, improvements, and inventions made by ATI.

- 10. Despite operating the electronic modules as specified, malfunctions or failures may occur before the end of their usual service life due to the current state of technology. Therefore, it is crucial for customer applications that require a high level of operational safety, especially in accident prevention or life-saving systems where the malfunction or failure of electronic modules could pose a risk to human life or health, to ensure that suitable measures are taken. The customer should design their application or implement protective circuitry or redundancy to prevent injury or damage to third parties in the event of an electronic module malfunction or failure.